# Contents

| Page | Section  | Title                                         |

|------|----------|-----------------------------------------------|

| 4    | 1.       | Introduction                                  |

| 5    | 1.1.     | System Architecture                           |

| 5    | 1.2.     | System Application                            |

| 6    | 2.       | Functional Description                        |

| 6    | 2.1.     | Display Part                                  |

| 6    | 2.1.1.   | Digital Input Interface                       |

| 6    | 2.1.2.   | Chroma Input                                  |

| 8    | 2.1.3.   | Horizontal Scaler                             |

| 8    | 2.1.4.   | Luma Contrast and Brightness                  |

| 8    | 2.1.5.   | Black Level Expander/Compressor (BLEC)        |

| 10   | 2.1.6.   | Luma Sharpness Enhancer (LSE)                 |

| 10   | 2.1.6.1. | Dynamic Peaking                               |

| 10   | 2.1.6.2. | Luma Transient Improvement (LTI)              |

| 11   | 2.1.7.   | Chroma Interpolation                          |

| 11   | 2.1.8.   | Chroma Transient Improvement                  |

| 11   | 2.1.9.   | Inverse Matrix and Digital RGB Processing     |

| 12   | 2.1.10.  | Picture Frame Generator                       |

| 12   | 2.1.11.  | Scan Velocity Modulation                      |

| 12   | 2.1.12.  | Non-linear Colorspace Enhancer (NCE)          |

| 13   | 2.2.     | Analog Back End                               |

| 13   | 2.2.1.   | Analog RGB Insertion                          |

| 14   | 2.2.2.   | Fast Blank Monitor                            |

| 14   | 2.2.3.   | Half Contrast Control                         |

| 14   | 2.2.4.   | CRT Measurement and Control                   |

| 16   | 2.2.5.   | Average Beam Current Limiter                  |

| 16   | 2.3.     | Synchronization and Deflection                |

| 16   | 2.3.1.   | Deflection Processing                         |

| 16   | 2.3.2.   | Security Unit for H-Drive                     |

| 18   | 2.3.3.   | Horizontal Phase Adjustment                   |

| 18   | 2.3.4.   | Vertical Synchronization                      |

| 19   | 2.3.5.   | Vertical and East/West Deflection             |

| 19   | 2.3.6.   | Vertical Zoom                                 |

| 20   | 2.3.7.   | EHT Compensation                              |

| 20   | 2.3.8.   | Protection Circuitry                          |

| 20   | 2.3.9.   | Display Frequency Doubling                    |

| 21   | 2.3.10.  | General Purpose D/A Converter                 |

| 21   | 2.3.11.  | Clock and Reset                               |

| 21   | 2.3.12.  | Reset and Power-On                            |

| 22   | 3.       | Serial Interface                              |

| 22   | 3.1.     | I <sup>2</sup> C-Bus Interface                |

| 22   | 3.2.     | I <sup>2</sup> C Control and Status Registers |

| 26   | 3.3.     | XDFP Control and Status Registers             |

| 40   | 3.3.1.   | Scaler Adjustment                             |

**DDP 3315C**

# Contents, continued

| Page | Section   | Title                                       |

|------|-----------|---------------------------------------------|

| 41   | 4.        | Specifications                              |

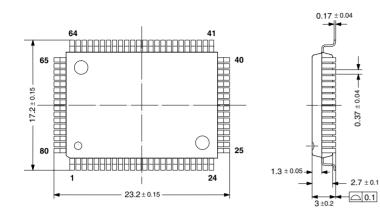

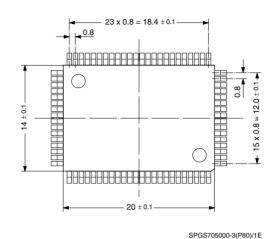

| 41   | 4.1.      | Outline Dimensions                          |

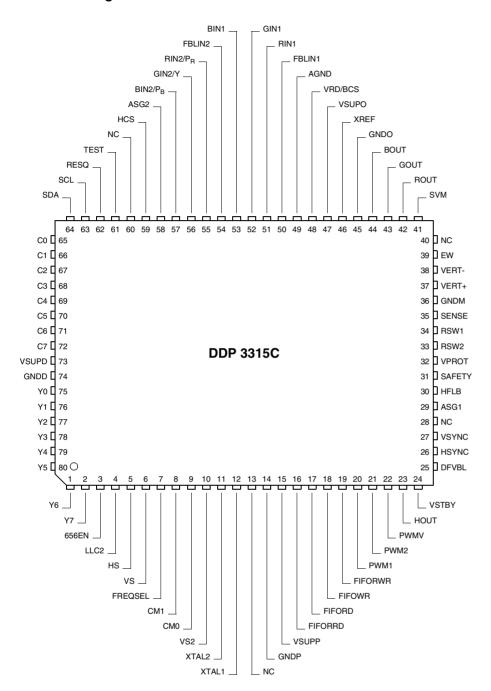

| 41   | 4.2.      | Pin Connections and Short Descriptions      |

| 44   | 4.3.      | Pin Descriptions                            |

| 47   | 4.4.      | Pin Configuration                           |

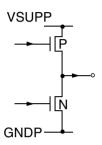

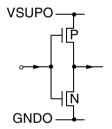

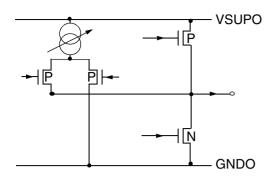

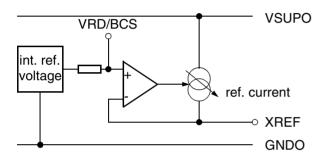

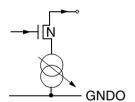

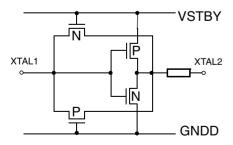

| 48   | 4.5.      | Pin Circuits                                |

| 50   | 4.6.      | Electrical Characteristics                  |

| 50   | 4.6.1.    | Absolute Maximum Ratings                    |

| 50   | 4.6.2.    | Recommended Operating Conditions            |

| 51   | 4.6.3.    | Recommended Crystal Characteristics         |

| 52   | 4.6.4.    | Characteristics                             |

| 52   | 4.6.4.1.  | General Characteristics                     |

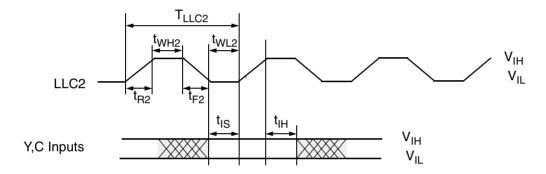

| 52   | 4.6.4.2.  | LLC2: Line-locked Clock Input               |

| 53   | 4.6.4.3.  | Luma, Chroma Inputs                         |

| 53   | 4.6.4.4.  | Digital Inputs, Static Pins                 |

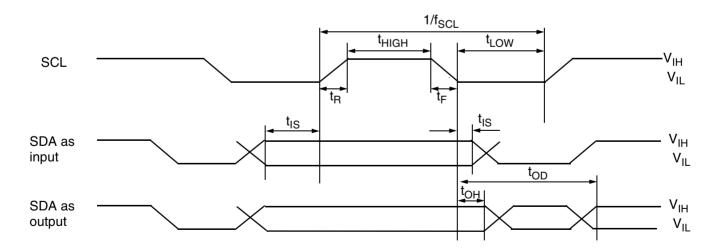

| 54   | 4.6.4.5.  | I <sup>2</sup> C-Bus Interface              |

| 55   | 4.6.4.6.  | Horizontal Flyback Input                    |

| 55   | 4.6.4.7.  | Sync Signals and PWM Outputs                |

| 55   | 4.6.4.8.  | Horizontal Drive Output                     |

| 55   | 4.6.4.9.  | Vertical Protection Input                   |

| 56   | 4.6.4.10. | Horizontal Safety Input                     |

| 56   | 4.6.4.11. | Vertical and East/West D/A Converter Output |

| 56   | 4.6.4.12. | East/West PWM Output                        |

| 56   | 4.6.4.13. | Sense A/D Converter Input                   |

| 57   | 4.6.4.14. | Analog RGB / YPBPR and FB Inputs            |

| 58   | 4.6.4.15. | Analog RGB Outputs, D/A Converters          |

| 60   | 4.6.4.16. | Scan Velocity Modulation Output             |

| 60   | 4.6.4.17. | DAC Reference, Beam Current Safety          |

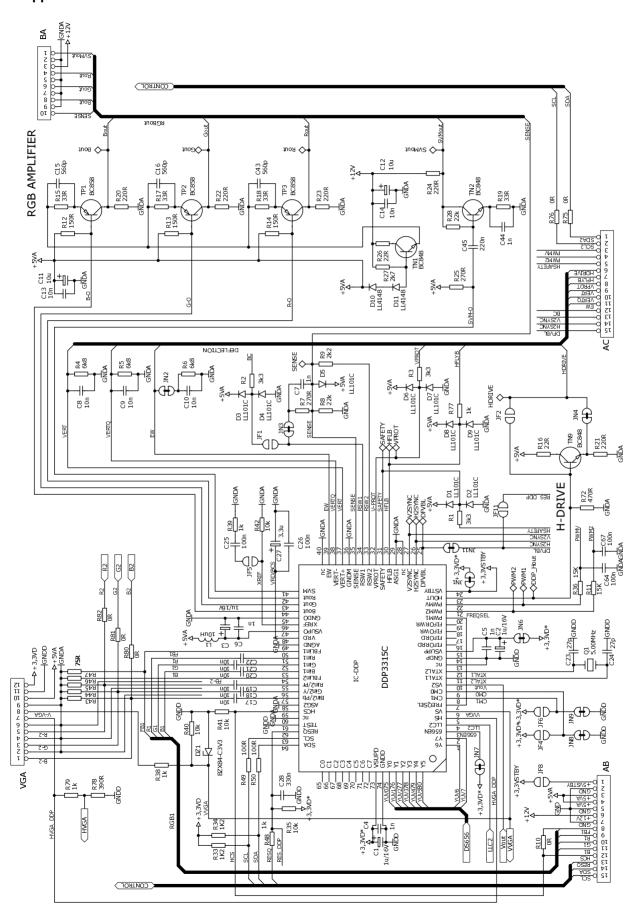

| 61   | 5.        | Application Circuit                         |

| 62   | 6.        | Data Sheet History                          |

# DDP 3315C Display and Deflection Processor

#### 1. Introduction

The DDP 3315C is a mixed-signal single-chip digital display and deflection processor, designed for high-quality backend applications in double scan and HDTV TV sets with 4:3 or 16:9 picture tubes. The interfaces qualify the IC to be combined with state of the art digital scan rate converters, as well as analog HDTV sources. The DDP 3315C contains the entire digital video component, deflection processing, and all analog interfaces to display the picture on a CRT. The main features are

# **Video Processing**

- linear horizontal scaling (0.25 ... 4), as well as nonlinear horizontal scaling "panorama vision"

- dynamic black level expander

- luma sharpness enhancement by dynamic peaking and luma transient improvement (LTI)

- color transient improvement (CTI)

- programmable RGB matrix

- black stretch, blue stretch, gamma correction via programmable Non-linear Colorspace Enhancer (NCE) on RGB

- two analog double scan inputs with fast blank (one RGB and one RGB/YC<sub>r</sub>C<sub>b</sub>/YP<sub>r</sub>P<sub>b</sub> selectable)

- average and peak beam current limiter

- automatic picture tube adjustment (cutoff, drive)

# **Deflection Processing**

- scan velocity modulation output

- digital EHT compensation for vertical / east-west

- vertical angle and bow correction

- differential vertical outputs

- vertical zoom via deflection adjustment

- horizontal and vertical protection circuit

- horizontal frequency for VGA/SVGA/1080I

- black switch off procedure

- supports horizontal and vertical dynamic focus

#### Miscellaneous

- selectable ITU-R 601 4:1:1 / 4:2:2 YC<sub>r</sub>C<sub>b</sub> input at 27/32 MHz or double scan ITU-R 656 input at 54 MHz line-locked clock

- crystal oscillator for horizontal safety

- picture frame generator

- hardware for simple 50/60 Hz to 100/120 Hz conversion (display frequency doubling)

- PQFP80 package, 5 V analog and 3.3 V digital supply

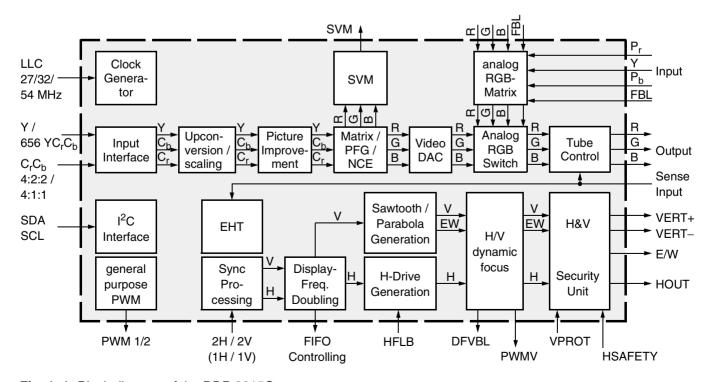

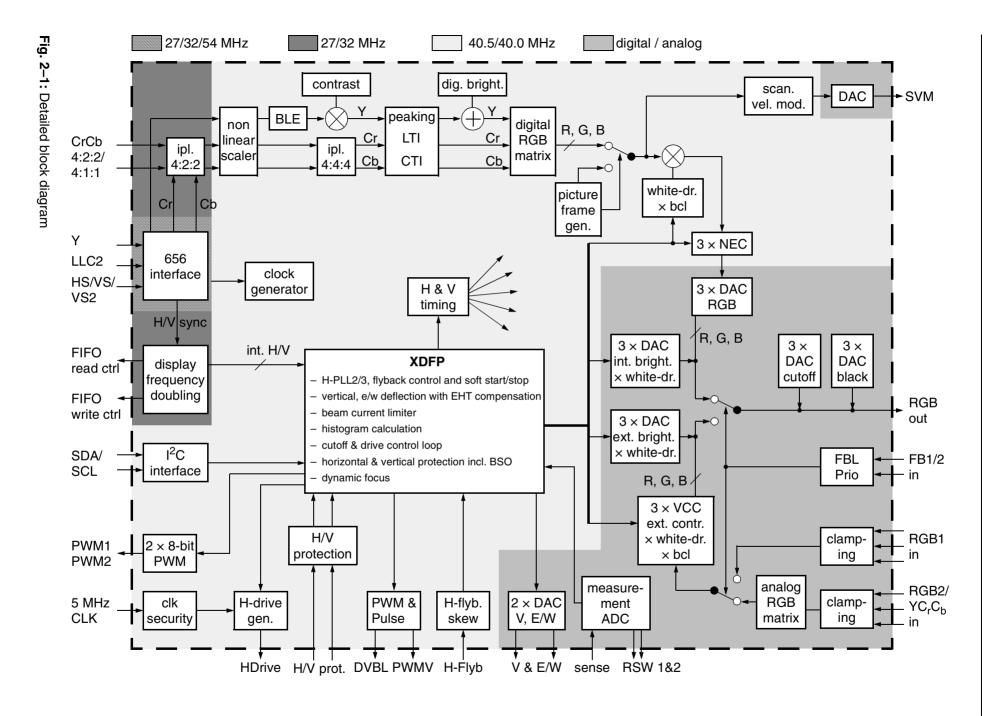

Fig. 1-1: Block diagram of the DDP 3315C

## 1.1. System Architecture

Fig. 1–1 shows the block diagram of the DDP 3315C.

A clock generator converts different external line locked clock rates to a common internal sample rate of ~40 MHz, in order to provide a higher horizontal resolution. The input interface accepts ITU-R 601 at 27 or 32 MHz and ITU-R 656 with encoded or external sync at 54 MHz. The horizontal scaler is used for the scan rate conversion and for the nonlinear aspect ratio conversion as well.

For the picture improvement, luma and chroma are processed separately. The luminance contrast ratio can be extended with a dynamic black level expander. In addition the frequency characteristic is improved by a transient improvement (LTI) and an adaptive dynamic peaking circuit. The peaking adapts to small AC amplitudes of high frequency parts, while large AC amplitudes are processed by the LTI. The chroma signal is enhanced with a transient improvement (CTI) with proper limitation to avoid wrong colors.

The full programmable RGB matrix covers control of color saturation and temperature. A digital white drive control is used to adjust the white balance and for the beam current limitation to prevent the CRT from overload. A non-linear colorspace enhancer (NCE) for RGB gives full flexibility for any amplitude characteristic.

High speed10-bit D/A converters are used to convert digital RGB to analog signals. Separate 9-bit D/A converters control brightness and cutoff. For picture tubes equipped with an appropriate yoke a scan velocity modulation (SVM) signal is calculated using a differentiated luminance signal.

Two analog sources can be inserted in the main RGB, controlled by separate fastblank (FBL) signals. Contrast and brightness are adjusted separately from main RGB. One input is dedicated to RGB for on screen dis-

play (OSD). The second input is processed with an analog RGB matrix to insert  $YC_bC_r/YP_bP_r$  or RGB with control of color saturation and programmable half contrast. The bandwidth of ~30 MHz guarantees pixel based graphics to be displayed with full accuracy.

All previously mentioned features are implemented in dedicated hardware. An integrated processor controls the horizontal and vertical deflection, tube measurement loops and beam current limitation. It is also used to calculate an amplitude histogram of the displayed image.

The horizontal deflection is synchronized with two numeric phase-locked loops (PLL) to the incoming sync. One PLL generates the horizontal timing signals, e.g. blanking and key-clamping. The second PLL adjusts the phase of the horizontal drive pulse with a subpixel accuracy less than 1 ns.

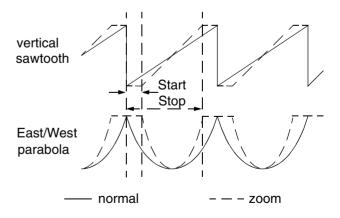

Vertical deflection and east/west correction waveforms are calculated as 6th order polynomials. This allows adjustment of an east/west parabola with trapezoidal, pincushion and an upper/lower corner correction (even for real flat CRT's), as well as a vertical sawtooth with linearity and S-correction. Scaling both waveforms, and limiting to fix amplitudes, performs a vertical zoom or compression of the displayed image. A field and line frequent control loop compensates picture content depending EHT distortions.

# 1.2. System Application

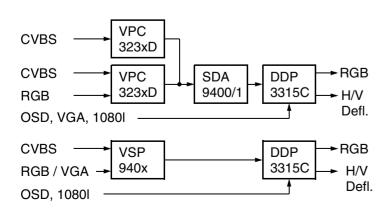

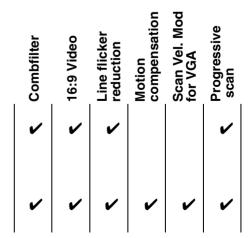

To form a complete TV set, the video backend must be complemented with additional components. Due to the flexible architecture of the DDP, it can be placed in various environments (see Fig. 1–2). Applications to display digital MPEG or PC graphics on large screens, inserting analog VGA sources in a TV as well as memory based image processing for 100/120 Hz or progressive scan rate conversion of TV sources, are intended with the DDP.

Fig. 1-2: DDP 3315C applications

#### 2. Functional Description

# 2.1. Display Part

The display part converts the digital  $YC_rC_b$  to analog RGB (see Fig. 2–1). In case of  $YC_rC_b$  4:1:1 an interpolation converts the digital input signal to  $YC_rC_b$  4:2:2 standard format. The 4:2:2  $YC_rC_b$  signal is processed by the horizontal scaler. In the luminance processing path, contrast and brightness adjustments and a variety of features, such as black level expander and luma sharpness enhancer, are provided. In the chrominance path, the  $C_rC_b$  signals are converted to 4:4:4 format and filtered by a color transient improvement circuit. The  $YC_rC_b$  signals are converted by a programmable matrix to RGB color space.

2.1.1. Digital Input Interface

The digital input interface supports

- 16 bit 4:2:2 YC<sub>r</sub>C<sub>b</sub> with separate H/V-syncs and clock (ITU-R-601 format)

- 12 bit 4:1:1 YC<sub>r</sub>C<sub>b</sub> with separate H/V-syncs and clock (ITU-R-601 format)

- 8 bit 4:2:2 YC<sub>r</sub>C<sub>b</sub> multiplexed with encoded or separate H/V-syncs and clock (ITU-R-656 format)

The data inputs Y0...Y7 and C0...C7 are clocked with the external clock LLC2. The clock frequency is selectable between 27 or 32 MHz for 12 and 16 bit data input and 54 MHz for 8 bit data input. The horizontal sync pulse at the HS pin should be an active video signal, which is not vertically blanked.

A clock generator converts the different external line locked clock rates to a common internal sample rate of approximately 40.5 MHz, in order to provide a fix bandwidth for all digital filters. Therefore the input data is sample rate converted to the common processing frequency by the horizontal scaler.

## 2.1.2. Chroma Input

The chroma input signal can either be  $YC_rC_b$  in 4:1:1 or in 4:2:2 format. For the digital signal processing the time-multiplexed chroma samples will be demultiplexed, synchronized with the signal at the HS Pin. The input formatter accepts either two's complement or binary offset code. Also the delay can be adjusted within a range of  $\pm 2$  input clocks relative to the luma signal; this doesn't effect the chroma multiplex.

Table 2-1: 4:1:1 chroma format

| Pin Name | Pixel Number                 |                              |                              |                              |  |  |  |

|----------|------------------------------|------------------------------|------------------------------|------------------------------|--|--|--|

|          | 1                            | 2                            | 3                            | 4                            |  |  |  |

| C7       | C <sub>b1</sub> <sup>7</sup> | C <sub>b1</sub> <sup>5</sup> | C <sub>b1</sub> <sup>3</sup> | C <sub>b1</sub> <sup>1</sup> |  |  |  |

| C6       | C <sub>b1</sub> <sup>6</sup> | C <sub>b1</sub> <sup>4</sup> | C <sub>b1</sub> <sup>2</sup> | C <sub>b1</sub> <sup>0</sup> |  |  |  |

| C5       | C <sub>r1</sub> <sup>7</sup> | C <sub>r1</sub> <sup>5</sup> | C <sub>r1</sub> <sup>3</sup> | C <sub>r1</sub> <sup>1</sup> |  |  |  |

| C4       | C <sub>r1</sub> <sup>6</sup> | C <sub>r1</sub> <sup>4</sup> | C <sub>r1</sub> <sup>2</sup> | C <sub>r1</sub> <sup>0</sup> |  |  |  |

Table 2-2: 4:2:2 chroma format

| Pin Name | Pixel Number                 |                              |                              |                              |  |  |  |

|----------|------------------------------|------------------------------|------------------------------|------------------------------|--|--|--|

|          | 1                            | 2                            | 3                            | 4                            |  |  |  |

| C7       | C <sub>b1</sub> <sup>7</sup> | C <sub>r1</sub> <sup>7</sup> | C <sub>b3</sub> <sup>7</sup> | C <sub>r3</sub> <sup>7</sup> |  |  |  |

| C6       | C <sub>b1</sub> <sup>6</sup> | C <sub>r1</sub> <sup>6</sup> | C <sub>b3</sub> <sup>6</sup> | C <sub>r3</sub> <sup>6</sup> |  |  |  |

| C5       | C <sub>b1</sub> <sup>5</sup> | C <sub>r1</sub> <sup>5</sup> | C <sub>b3</sub> <sup>5</sup> | C <sub>r3</sub> <sup>5</sup> |  |  |  |

| C4       | C <sub>b1</sub> <sup>4</sup> | C <sub>r1</sub> <sup>4</sup> | C <sub>b3</sub> <sup>4</sup> | C <sub>r3</sub> <sup>4</sup> |  |  |  |

| С3       | C <sub>b1</sub> <sup>3</sup> | C <sub>r1</sub> <sup>3</sup> | C <sub>b3</sub> <sup>3</sup> | C <sub>r3</sub> <sup>3</sup> |  |  |  |

| C2       | C <sub>b1</sub> <sup>2</sup> | C <sub>r1</sub> <sup>2</sup> | C <sub>b3</sub> <sup>2</sup> | $C_{r3}^{2}$                 |  |  |  |

| C1       | C <sub>b1</sub> <sup>1</sup> | C <sub>r1</sub> <sup>1</sup> | C <sub>b3</sub> <sup>1</sup> | C <sub>r3</sub> <sup>1</sup> |  |  |  |

| CO       | C <sub>b1</sub> <sup>0</sup> | C <sub>r1</sub> 0            | C <sub>b3</sub> <sup>0</sup> | C <sub>r3</sub> <sup>0</sup> |  |  |  |

**Note:**  $C_x^y$ ; x = pixel number; y = bit number

#### 2.1.3. Horizontal Scaler

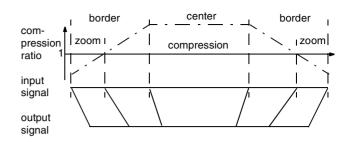

The horizontal scaler supports linear or nonlinear horizontal scaling of the digital input video signal in the range of 0.25 to 4. Nonlinear scaling, also called "panorama vision", provides a geometrical distortion of the input picture. It is used to fit a picture with 4:3 format on a 16:9 screen by stretching the picture geometry at the borders. Also, the inverse effect can be produced by the scaler.

A summary of scaler modes is given in Table 2-3.

Table 2-3: Scaler modes

| Mode                  | Scale<br>Factor         | Description                                                                                                    |

|-----------------------|-------------------------|----------------------------------------------------------------------------------------------------------------|

| Panorama<br>4:3 →16:9 | non<br>linear<br>compr. | 4:3 source displayed on a16:9 tube, borders distorted                                                          |

| Panorama<br>4:3 → 4:3 | non<br>linear<br>zoom   | Letterbox source (PAL+)<br>displayed on a 4:3 tube,<br>vertical overscan,<br>borders distorted,<br>no cropping |

| 27 → 40.5 MHz         | 1.5<br>linear           | sample rate conversion<br>from external to internal<br>pixel clock                                             |

| 32 → 40 MHz           | 1.25<br>linear          | sample rate conversion<br>from external to internal<br>pixel clock                                             |

# 2.1.4. Luma Contrast and Brightness

The luminance signal is multiplied by a factor of 0...2 in 64 steps. Simultaneously the matrix coefficients are adapted to preserve the color saturation (see Section 2.1.9. on page 11)

With a contrast adjustment of 32 (gain=1) the signal can be shifted by  $\pm 100\%$  of its maximal amplitude with the digital brightness value. This is for adjustment of the headrooms for under- and overshoot. After the brightness addition, the negative going signals are limited to zero. It is desirable to keep a small positive offset with the signal to prevent undershoots produced by the peaking from being cut.

# 2.1.5. Black Level Expander/Compressor (BLEC)

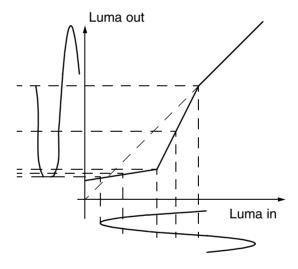

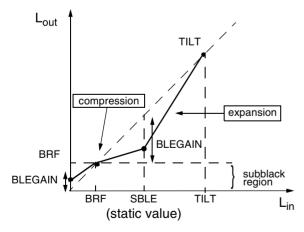

The black level expander/compressor modifies the luminance signal with an adjustable non-linear function to enhance the contrast of the picture (see Fig. 2–2). Dark areas are stretched to black, while bright areas remain unchanged. Advantageously, this black level processing is performed dynamically and only if it will be most noticeable to the viewer.

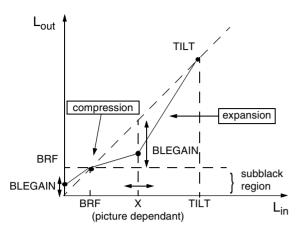

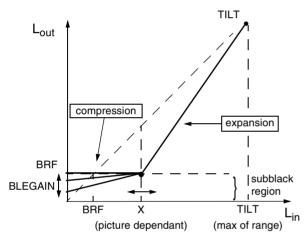

The BLEC supports the following modes (see Fig. 2–3):

- dynamic BLEC mode

This is the normal operation mode. The expansion depends on a pixel analysis.

- auto contrast mode

In the auto contrast mode, the TILT point is shifted to its maximum.

- static BLEC mode

In the static mode, the expansion depends on a programmable value SBLE.

Fig. 2-2: BLEC function

# **Dynamic BLEC mode**

# **Autocontrast mode**

# Static BLEC mode

Fig. 2-3: BLEC modes

## 2.1.6. Luma Sharpness Enhancer (LSE)

Sharpness is one of the most critical features for optimum picture quality. This important processing is performed in the LSE circuitry of DDP 3315C.

It consists of the dynamic peaking, the luma transient improvement (LTI) and an adaptive mixer. The luma input signal is processed in the peaking and LTI block in parallel. Both output signals are combined in the mixer depending on the selected LSE characteristic.

# 2.1.6.1. Dynamic Peaking

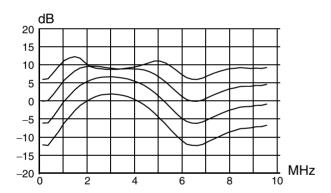

The dynamic peaking improves the details of a picture by contour emphasis. It adapts to the amplitude and the frequency of the input signal. Small detail amplitudes are sharpened, while large detail amplitudes stay nearly unmodified.

The max. dynamic range of small high-frequency detail amplitudes is 14 dB. The dynamic range of large detail amplitudes is limited automatically by a non-linear function that does not create any visible alias components (see Fig. 2–4).

Fig. 2-4: Dynamic peaking frequency response

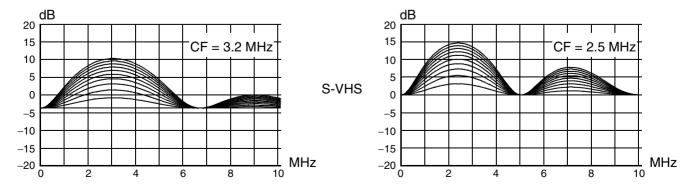

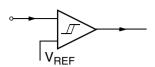

The peaking features two selectable center frequencies of 2.5 MHz or 3.2 MHz (see Fig. 2–5). An adjustable coring threshold prevents the enhancement of small noise amplitudes.

# 2.1.6.2. Luma Transient Improvement (LTI)

For small detail amplitudes the dynamic peaking is the most appropriate processing to improve the sharpness. However, for large amplitudes even small overand/or undershoots of the peaking are too annoying.

The luma transient improvement enhances the slope of picture detail without these effects by a non-linear processing. The contour correction signal calculated in this block, is limited to the adjacent extreme values to prevent over- and undershoots (see Fig. 2–7).

The LTI features an adjustable gain control and an adjustable coring threshold to prevent the enhancement of small noise amplitudes.

The contour correction signals of the dynamic peaking and the LTI block are combined adaptively to achieve best sharpness impression.

Fig. 2-5: Dynamic peaking frequency response in S-VHS (all frequencies refers to a 50/60 Hz video signal)

## 2.1.7. Chroma Interpolation

In case of YC<sub>r</sub>C<sub>b</sub> 4:1:1 input format, the digital input signal is converted to 4:2:2 format by an interpolation filter working at the input pixel clock frequency.

The signal is passed to the scaler in  $YC_rC_b$  4:2:2 format, in order to convert the incoming pixel clock frequency (27/32 MHz) to the internal frequency (40.5/40 MHz).

A linear phase interpolator is used to convert the chroma sampling rate from 4:2:2 to 4:4:4. The frequency response of the interpolator is shown in Fig. 2–6. All further processing is carried out at the full sampling rate.

**Fig. 2–6:** Frequency response of the chroma 4:2:2 to 4:4:4 interpolation filter

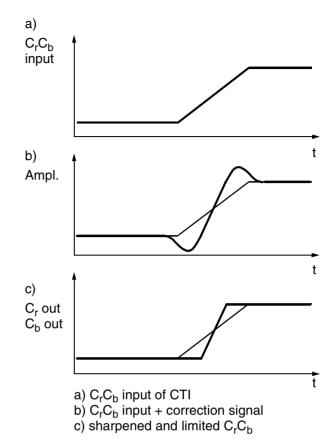

## 2.1.8. Chroma Transient Improvement

The intention of this block is to enhance the chroma resolution. A correction signal is calculated by differentiation of the color difference signals. The differentiation can be selected according to the signal bandwidth, e.g. for PAL/NTSC/SECAM or digital component signals, respectively. The amplitude of the correction signal is adjustable. Small noise amplitudes in the correction signal are suppressed by an adjustable coring circuit. To eliminate "wrong colors", which are caused by over and undershoots at the chroma transition, the sharpened chroma signals are limited to a proper value automatically (see Fig. 2–7).

Fig. 2-7: Luma/chroma transient improvement

# 2.1.9. Inverse Matrix and Digital RGB Processing

Six multipliers in parallel perform the matrix multiplication to transform the  $C_r$  and  $C_b$  signals to R-Y, B-Y, and G-Y. The initialization values for the matrix are computed from the standard ITU-R matrix:

$$\begin{bmatrix} R \\ G \\ B \end{bmatrix} = \begin{bmatrix} 1 & 0 & 1,402 \\ 1 & -0,345 & -0,713 \\ 1 & 1,773 & 0 \end{bmatrix} \times \begin{bmatrix} Y \\ Cb \\ Cr \end{bmatrix}$$

The multipliers are also used to adjust color saturation and picture contrast. The matrix computes:

$$\begin{bmatrix} R \\ G \\ B \end{bmatrix} = \frac{CTM}{32} \times \frac{SATM}{32} \times \frac{1}{64} \times \begin{bmatrix} MR1M & MR2M \\ MG1M & MG2M \\ MB1M & MB2M \end{bmatrix} \times \begin{bmatrix} Cb \\ Cr \end{bmatrix} + \left( \frac{CTM}{32} \times Y \right)$$

#### 2.1.10. Picture Frame Generator

The picture frame generator produces a programmable border surrounding the displayed image. By swapping the start and stop parameters a windows is produced instead.

The color of the complete border is stored in a programmable frame register. The format is 3x4 bit RGB. The contrast can be adjusted separately.

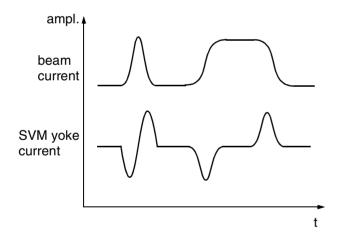

# 2.1.11. Scan Velocity Modulation

Picture tubes equipped with an appropriate yoke can use the Scan Velocity Modulation signal to vary the speed of the electron gun during the entire video scan line dependent upon its content. Transitions from dark to bright will first speed up and then slow down the scan; vice versa for the opposite transition (see Fig. 2–8).

The signal delay is adjustable by  $\pm 3.5$  clocks in half-clock steps in respect to the analog RGB output signals. This is useful to match the different groupdelay of analog RGB amplifiers to the one for the SVM yoke current.

Fig. 2-8: SVM signal waveform

# 2.1.12. Non-linear Colorspace Enhancer (NCE)

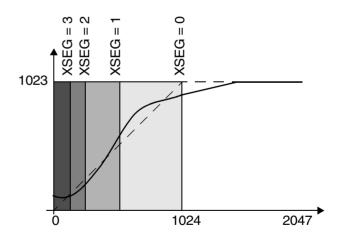

This block allows all kinds of non-linear functions such as gamma correction, blue stretch, peak white limitation, for each path R,G and B separately. In the following only one path is described (see Fig. 2–9).

Whereas the full input range of the NCE is 0...2047, the non-linear function is a combination of 8  $I^2C$  programmable linear segments  $S_0$  to  $S_7$  lying in the range 0...1023. Beyond 1023, the non-linear curve consists of the continuation of  $S_7$  and the limitation to 1023.

If the segments  $S_0$  to  $S_7$  cover the full input range from 0 to 1023 they can be placed on a grid of 32. In the case where all segments lie in a smaller range, the following modes with higher precision are available.

Table 2–4: Input range and grid covered by S<sub>0</sub>...S<sub>7</sub>

| Mode     | Range | Grid |

|----------|-------|------|

| XSEG = 0 | 01023 | 32   |

| XSEG = 1 | 0511  | 16   |

| XSEG = 2 | 0255  | 8    |

| XSEG = 3 | 0127  | 4    |

Fig. 2-9: NCE characteristic

## 2.2. Analog Back End

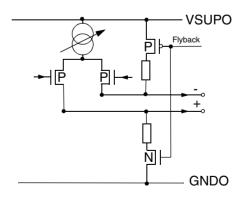

The digital RGB signals are converted to analog RGB by three 10-bit digital to analog converters (DAC).

Each RGB signal has two additional DACs with 9-bit resolution to adjust analog brightness (40% of the full RGB range) and cutoff / black level (60% of the full RGB range). An additional fixed current is applied for the blanking level.

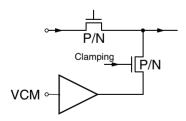

The back-end supports the insertion of two external analog component signals, e. g. OSD or analog HDTV. These signals are clamped, processed in an analog matrix (RGB2), converted by a voltage/current converter (VCC), and inserted into the main RGB by the fast blank switch.

The analog RGB outputs are current outputs with current-sink characteristics. The maximum current drawn by the output stage is obtained with peak white RGB.

The controlling of the whitedrive/analog brightness and also the external contrast and brightness adjustments is done via the internal Processor.

#### 2.2.1. Analog RGB Insertion

The DDP 3315C supports the insertion of

- 2 external analog RGB signals or

- 1 external analog RGB and 1 external YC<sub>r</sub>C<sub>b</sub>/YP<sub>r</sub>P<sub>b</sub> signal.

Each component signal is clamped, converted to RGB if required, and inserted into the main RGB by the fast blank switch. The external component signals are adjustable independently as regards DC level (brightness) and magnitude (contrast).

The second external analog input is processed by an analog matrix with control of color saturation and programmable half contrast.

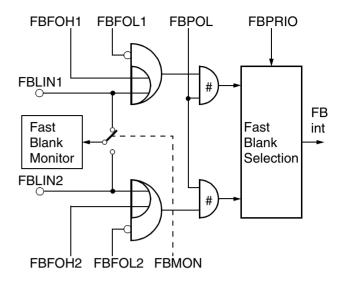

Fig. 2-10: Fast Blank selection logic

Over-/underlay of the external component signal and the main RGB signal depends on the fast blank input signals and the corresponding I<sup>2</sup>C-register (see Fig. 2–10). Both fast blank inputs must be either active low or active high.

All signals for analog component insertion (RIN1/2, GIN1/2, BIN1/2, FBLIN1/2, HCS) must be synchronized to the digital RGB.

External YC<sub>r</sub>C<sub>b</sub>/YP<sub>r</sub>P<sub>b</sub> signals are converted to RGB by the following matrix.

Table 2-5: Matrix coefficients for 480P and 1080I

| $\begin{bmatrix} R \\ G \\ B \end{bmatrix} = \begin{bmatrix} 1 & 0 & K_{rr} \\ 1 & K_{gb} & K_{gr} \\ 1 & K_{bb} & 0 \end{bmatrix} \otimes \begin{bmatrix} Y \\ C_b \\ C_r \end{bmatrix}$ |                                  |                     |                 |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------|-----------------|--|--|--|--|--|--|--|

|                                                                                                                                                                                           | I <sup>2</sup> C                 | Setting             |                 |  |  |  |  |  |  |  |

| MAT-<br>Type                                                                                                                                                                              | 010                              | 100                 | 0 0 1           |  |  |  |  |  |  |  |

| Standard                                                                                                                                                                                  | ITU-R 601 / 480P<br>(SMPTE 293M) | 1080I<br>(ITU-R709) | RGB<br>(Bypass) |  |  |  |  |  |  |  |

| K <sub>rr</sub>                                                                                                                                                                           | 1.402                            | 1.575               | 0               |  |  |  |  |  |  |  |

| K <sub>gb</sub>                                                                                                                                                                           | -0.344                           | -0.187              | 0               |  |  |  |  |  |  |  |

| K <sub>gr</sub>                                                                                                                                                                           | -0.7144                          | -0.468              | 0               |  |  |  |  |  |  |  |

| K <sub>bb</sub>                                                                                                                                                                           | 1.773                            | 1.856               | 0               |  |  |  |  |  |  |  |

#### 2.2.2. Fast Blank Monitor

The presence of external analog RGB sources can be detected by means of a fast blank monitor. The status of the selected fast blank input can be monitored via an I<sup>2</sup>C register. There is a 2 bit information, giving static and dynamic indication of a fast blank signal. The static bit is directly reading the fast blank input line, whereas the dynamic bit is reading the status of a flip flop triggered by the negative edge of the fast blank signal.

With this monitor logic it is possible to detect if there is an external RGB source active and if it is a full screen insertion or only a box. The monitor logic is connected directly to the FBLIN1 or FBLIN2 pin. Selection is done via  $\rm I^2C$  register.

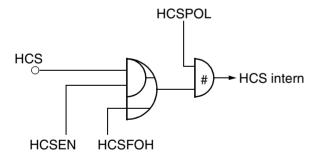

#### 2.2.3. Half Contrast Control

Insertion of transparent text pages or OSD onto the video picture is often difficult to read, especially if the video contrast is high. The DDP 3315C features a contrast reduction of the video background of 30 or 50% by means of a half contrast input (HCS pin). This input can be supplied with a fast switching signal (similar to the fast blank input), typically defining a rectangular box. Inside this box the video picture is displayed with reduced contrast, while the analog component signals are still displayed with full contrast.

Fig. 2–11: Half Contrast switch logic

#### 2.2.4. CRT Measurement and Control

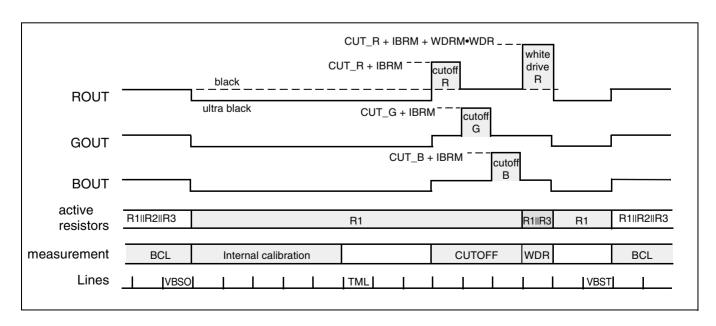

In order to define accurate color on different CRT displays, the cut-off and white drive settings have to be adjusted depending on the characteristic of CRT phosphor. To guarantee correct colors during the for the lifetime of the display, a build in automatic tube control loop measures and adjusts the black level on every field and white point every third field.

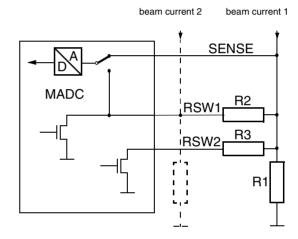

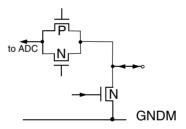

The display processor is equipped with an 9/12-bit PDM-ADC for all picture tube measuring purposes. This MADC is connected to the SENSE input pin, the input range is 0 to 2.6 V.

Cutoff and white drive current measurement are carried out with 8-bit resolution during the vertical blanking interval. The current range for cutoff measurement is set by connecting the sense resistor R1 to the SENSE input. Due to the fact of a 1:10 relation between cutoff and white drive current the range select 2 output (RSW2) becomes active for the white drive measurement and connects R3 in parallel to R1, thus determining the correct current range. During the active picture, the MADC is used for the average beam current limiter with a 12-bit resolution. Again a different measurement range is selected with active range select 1&2 outputs (RSW1&RSW2) connecting R2 in parallel to R3 and R1. See Fig. 2–12 and Fig. 2–13 for the corresponding timing.

These measurements are typically done at the summation point of the picture tube cathode currents.

Another method uses two different current measurements:

- The range switch 1 pin (RSW1) can be used as a second sense input, selectable by software. In this case, the cutoff and white drive currents are measured as before at the SENSE input.

- The active picture measurement can be done with the second sense input (RSW1). The signal may come (via a proper interface) from the low end of the EHT coil (CRT anode current). In this case, the resistor R2 in Fig. 2–12 has to be removed.

The picture tube measurement returns results on every field for:

- cutoff R

- cutoff G

- cutoff B

- white drive R or G or B (sequentially)

Thus a cutoff control cycle for RGB requires one field only, while a complete white drive control cycle requires three fields. During cutoff and whitedrive measurement, the average beam current limiter function (see Section 2.2.5.) is switched off. The amplitude of the cutoff and white drive measurement lines can be programmed separately with IBRM and WDRM (see Fig. 2–13). The start line for the tube measurement (cutoff red) can be programmed via I<sup>2</sup>C-bus (TML).

The built-in control loop for cutoff and white drive can operate in three different modes selected by CUT(WDR) GAIN and CUT(WDR) DIS.

- The user control mode is selected by setting CUT(WDR)\_GAIN = 0. In this mode the registers CUT(WDR)\_R/G/B are used as direct control values for cutoff and drive. If the measurement lines are enabled (CUT(WDR)\_DIS = 0) the user can read the measured cutoff & white drive values in the CUTOFF(WDRIVE)\_R/G/B registers. An external software can now control the settings of the CUT(WDR)\_R/G/B registers.

- The automatic mode is selected by setting CUT(WDR)\_GAIN > 0 and CUT(WDR)\_DIS = 0. In this mode, the registers CUT(WDR)\_R/G/B are used as reference for the measured values (CUT-OFF(WDRIVE)\_R/G/B). The calculated error is used with a small hysteresis (1.5%) to adjust cutoff and drive. The higher the loopgain (CUT(WDR)\_GAIN) the smaller the time constant for the adjustment.

If the automatic mode was once enabled (CUT(WDR)\_GAIN > 0), the control loop can be stopped by setting CUT(WDR)\_DIS = 1. In this mode the calculated cutoff and drive values will no longer be modified and the measurement lines are suppressed. Changes of the reference values (CUT(WDR)\_R/G/B) have no effect.

If one of the calculated red, green or blue white drive values exceeds it's maximal possible value (WDR\_R/G/B>511), the white balance gets misadjusted. An automatic drive saturation avoidance prevents from this effect (WDR\_SAT = 1). If one drive value exceeds the maximum allowed threshold (MAX\_WDR) the amplitude of the white drive measurement line will be increased and decreased if one of them goes below the fixed threshold 475.

Fig. 2-12: MADC range switch

Fig. 2-13: MADC measurement timing

#### 2.2.5. Average Beam Current Limiter

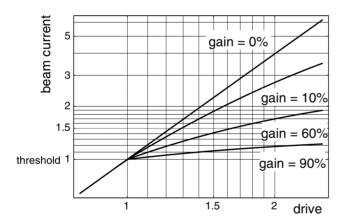

The average beam current limiter (BCL) works on both the digital  $YC_rC_b$  input and the inserted analog RGB signals by using either the sense input or the RSW1 input for the beam current measurement. The BCL uses a different filter to average the beam current during the active picture resulting in a 12-bit resolution. The filter bandwidth is approximately 4 kHz.

The beam current limiter allows the setting of a threshold current, a gain and an additional time constant. If the beam current is above the threshold, the excess current is low-pass filtered with the according gain and time constant. The result is used to attenuate the RGB outputs by adjusting the white drive multipliers for the internal (digital) RGB signals, and the analog contrast multipliers for the analog RGB inputs, respectively. The lower limit of the attenuator is programmable, thus a minimum contrast can always be set. If the minimum contrast is reached, the brightness will be decreased to a programmable minimum as well. Typical characteristics of the BCL for different loop gains are shown in Fig. 2–14; for this example the tube has been assumed to have square law characteristics.

**Fig. 2–14:** Beam current limiter characteristics: beam current output vs. drive

#### 2.3. Synchronization and Deflection

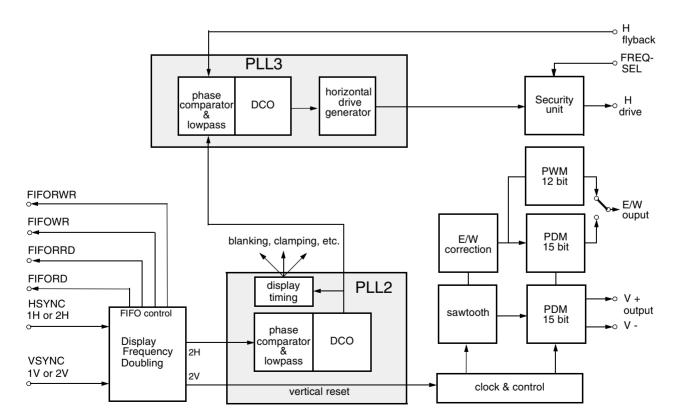

## 2.3.1. Deflection Processing

The deflection processing generates the signals for the horizontal and vertical drive (see Fig. 2–15). This block contains two numeric phase-locked loops and a security unit:

- PLL2 generates the horizontal and vertical timing, e.g. blanking, clamping and sync signals. Phase and frequency are synchronized by the incoming sync signals.

- PLL3 adjusts the phase of the horizontal drive pulse and compensates for the delay of the horizontal output stage.

- The security unit observes the H-Drive output signal. With an external 5 MHz reference clock this unit controls the H-drive "off time" and period. In case of an incorrect H-drive signal the security unit generates a free running h-drive signal divided down from the 5 MHz reference clock.

The DDP 3315C is able to synchronize to various horizontal frequencies, even VGA frequencies. Supported horizontal input frequencies are listed in Table 2–6.

# 2.3.2. Security Unit for H-Drive

The security unit observes the H-Drive output signal with an external 5 MHz reference clock. For different horizontal frequencies the security unit uses different ranges to control the H-Drive signal. Selecting a specific horizontal frequency via I<sup>2</sup>C-Register HFREQ, automatically switches to the corresponding security range. The control ranges are listed in Table 2–6.

The window of the control range has to lie within a main control window which is selectable with the FREQSEL input pin. With a low signal at this pin the main control range is 28.8... 34.4  $\mu s$  and with a high signal the main control range is 25.6... 29.2  $\mu s$ . This is to prevent male functions if the horizontal deflection stage is prepared for VGA frequencies.

The Horizontal Drive Output can be forced to the high level during Flyback. This means, the falling edge of the drive pulse is earliest possible at the end of the flyback pulse. This function can be enabled via the I2C bus (EFLB).

Table 2-6: Supported horizontal input frequencies

| Supply<br>Clock<br>(MHz) | Pixels per<br>line<br>Supply clk | Main<br>clock<br>(in MHz) | Pixels per<br>line<br>Main clk | horiz. freq.<br>(Hz) | Minimum H-<br>Drive period<br>(in μs) | Maximum<br>H-Drive<br>period<br>(in μs) | HFREQ<br>(I <sup>2</sup> C) |

|--------------------------|----------------------------------|---------------------------|--------------------------------|----------------------|---------------------------------------|-----------------------------------------|-----------------------------|

| 27                       | 864                              | 40.5                      | 1296                           | 31.24968             | 29.60                                 | 34.40                                   | 000                         |

| 27                       | 858                              | 40.5                      | 1287                           | 31.46853             | 29.60                                 | 34.40                                   | 010                         |

| 27                       | 800                              | 40.5                      | 1200                           | 33.750               | 28.80                                 | 30.60                                   | 100                         |

| 27                       | 768                              | 40.5                      | 1152                           | 35.15625             | 27.80                                 | 29.20                                   | 001                         |

| 27                       | 720                              | 40.5                      | 1080                           | 37.500               | 25.60                                 | 28.00                                   | 101                         |

| 27                       | 712                              | 40.5                      | 1068                           | 37.92135             | 25.60                                 | 28.00                                   | 110                         |

| 32                       | 1024                             | 40.0                      | 1280                           | 31.24952             | 29.60                                 | 34.40                                   | 000                         |

| 32                       | 944                              | 40.0                      | 1180                           | 33.89776             | 28.80                                 | 30.60                                   | 100                         |

| 32                       | 912                              | 40.0                      | 1140                           | 35.08747             | 27.80                                 | 29.20                                   | 001                         |

| 32                       | 852                              | 40.0                      | 1065                           | 37.55869             | 25.60                                 | 28.00                                   | 101                         |

| 32                       | 844                              | 40.0                      | 1055                           | 37.91469             | 25.60                                 | 28.00                                   | 110                         |

| 40.5                     | 1296                             | 40.5                      | 1296                           | 31.24968             | 29.60                                 | 34.40                                   | 000                         |

Fig. 2–15: Deflection processing block diagram

#### 2.3.3. Horizontal Phase Adjustment

This section describes a simple way to get a correct horizontal frame position and clamp window for analog RGB insertion.

- 1. For a correct scaler function in panorama/waterglass mode the digital input data should be centered to the active video input signal.

- 2. The clamping pulse for analog RGB insertion can be adjusted to the pedestal of the input signal with POFS2.

- 3. The horizontal raster position of the analog inserted RGB1/2 signal can be set to the desired frame position with POFS3.

- 4. The horizontal position of the digital RGB signal can be shifted to the left and right with NEWLIN. Following values allowed in respect to POFS2:

90 < (POFS2+NEWLIN) − (clk • SFIF) < 580 clk = 3 @ LLC2 = 27 MHz

clk = 2,5 @ LLC2 = 32 MHz

5. Now the positioning of horizontal blanking and the picture frame generator can be done.

## 2.3.4. Vertical Synchronization

The number of lines per field can be adjusted by software (LPFD). This number is used to calculate the vertical raster. The DDP synchronizes only to a vertical sync within a programmable detection window (LPFD  $\pm$  VSYNCWIN). If there is no vsync the DDP runs with maximum allowed lines and if the vertical frequency is to high it runs with minimum allowed lines. The smaller the detection window the slower the DDP gets synchronized to the incoming vertical sync. In case of an interlaced input signal it is possible to display both fields at the same raster position by setting R\_MODE to 1 or 2.

An automatic field length adaptation can be selected (VA\_MODE). In this case the vertical raster will be calculated according to the counted number of lines per field instead from LPFD. This is useful for video recorder search mode when the number of lines per field does not comply with the standard, or if you want to use a common value of LPFD for PAL and NTSC (e.g.: LPFD = 290; VSYNCWIN = 54).

#### 2.3.5. Vertical and East/West Deflection

The calculations of the Vertical deflection and East/ West correction waveforms are done in the internal processor. They are described as polynomials in x, where x varies from  $-0.5 \bullet zoom$  to  $+0.5 \bullet zoom$  for one field. For zoom>1, the range is limited between -0.5 and +0.5.

The vertical deflection waveform is calculated as follows (without EHT compensation):

$$V = vpos + ampl(x + lin(x^2 - offset) + scor \cdot x(x^2 - offset))$$

VPOS defines the vertical raster positionAMPL is the vertical raster amplitude

$(zoom \ge 1)$

- LIN is the linearity coefficient

SCOR is the coefficient for S-correction

OFFSET is an internal parameter

The vertical sawtooth signal will be generated from a differential current D/A converter and can drive a DC coupled power stage. In order to get a faster vertical retrace timing, the output current of the vertical D/A-converter can be increased during the retrace for a programmable number of lines (FLYBL). The range between the end of the flyback and the beginning of the raster is also programmable (HOLDL).

The East/West deflection waveform, generated from a single ended D/A converter, is given with the equation:

$$E/W = width + trapez \cdot x + cush \cdot x^2 + corner \cdot x^4$$

- WIDTH is a DC value for the picture width

TRAPEZ is the trapezoidal correction

CUSH is the pincushion correction

CORNU is the upper corner correction

CORNL is the lower corner correction

Fig. 2–16: Vertical and East/West deflection waveforms

# 2.3.6. Vertical Zoom

With vertical zoom the DDP 3315C is able to display different aspect ratios of the source signal on tubes with 4:3 or 16:9 aspect ratio by adapting the corresponding raster.

Fig. 2-17: Vertical zoom

#### 2.3.7. EHT Compensation

The vertical deflection waveform can be scaled according the average beam current. This is used to compensate the effects of electric high tension changes due to beam current variations. EHT compensation for East/West deflection is done with an offset corresponding to the average beam current. The time constant of this process is free programmable with a resolution of 18 bit. Both corrections can be enabled separately. The maximum scaling coefficient for vertical deflection is  $1\pm x$  and the maximum offset for east/ west is y, where x, y are adjustable from 0 to 0.25. The horizontal phase at the output HOUT can be influenced according to the average beam current in a range of  $\pm 1.5~\mu s$ .

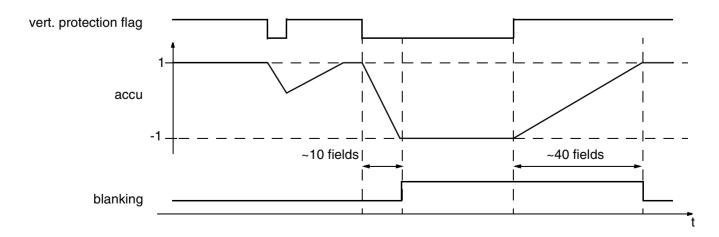

## 2.3.8. Protection Circuitry

Picture tube and drive stage protection is provided through the following measurements:

- Vertical protection input: this pin watches the vertical sawtooth signal. In every field the sawtooth must descend below the lower threshold A and ascend above the upper threshold B. In this case the protection flag is set (sawtooth o.k.). If an error occurs the protection flag is cleared.

After a programmable number of fields with cleared flag the RGB drive signals are blanked. The blanking is cancelled if the flag is set a programmable number of lines (see Fig. 2–18)

- Drive shutoff during flyback: this feature can be selected by software (EFLB)

- Safety input pin: this pin has two thresholds. The lower threshold A watches for a positive edge in every line, and the upper threshold B must not be overshoot, otherwise the RGB signals are blanked and a soft stop can be performed (HPROT\_SS). Both thresholds have a small hysteresis.

# 2.3.9. Display Frequency Doubling

The DDP 3315C handles single or double vertical and horizontal input frequencies. The display frequency doubling is used when single H/V frequencies are applied and an external FIFO for scan rate conversion is used. In this mode it is mandatory to supply an active video signal to the HS pin, which is not vertical blanked.

Three different raster modes are selectable via I2C bus:

A A' B' B (normal operation)

A A B B (improved vertical resolution)

A A B' B' (non interlaced)

A/B means field A/B in original raster position and A'/B' means field A/B in the opposite raster position.

A minimum field length filter can be switched on (DFD-FILT) to write only the smallest field length of the past up to four fields into the memory. This prevents read before write errors in signals with a strong changing field length (e.g. VCR signals).

Fig. 2–18: Vertical protection timing

# 2.3.10. General Purpose D/A Converter

There are two D/A converters using pulse width modulation. The resolution is 8 bit and the clock frequency is 20.25 MHz. The outputs are push pull types. For a ripple-free output voltage a first order lowpass filter with a corner frequency < 120 Hz should be applied.

The D/A converters are adjusted via the I<sup>2</sup>C bus. They can be used to generate two DC voltages, for example for horizontal raster position, raster tilt or just as switching outputs, when the values 0 and 255 are selected.

#### 2.3.11. Clock and Reset

The DDP 3315C supports 27, 32, 40.5 and 54 MHz line-locked clock rates. This external clock rate is converted internally to a clock rate of 40.5 or 40 MHz by means of a PLL. Selection of external clock frequency is done with Pins CM1 and CM0. See Table 2–7 for clock frequency selection. To ensure lock of PLL a reset pulse of at least 500  $\mu s$  must be applied after power up.

Table 2-7: Clock frequency selection

| 656EN | CM1 | СМО | LLC2     |

|-------|-----|-----|----------|

| 0     | 0   | 0   | 27 MHz   |

| 0     | 0   | 1   | 32 MHz   |

| 0     | 1   | 0   | 40.5 MHz |

| 1     | 0   | 0   | 54 MHz   |

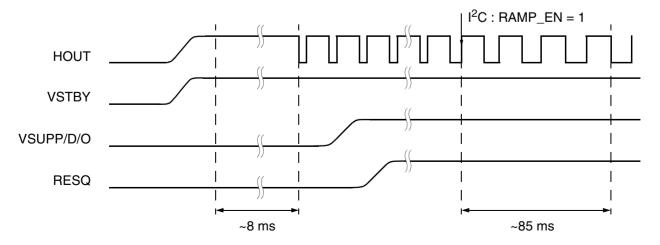

#### 2.3.12. Reset and Power-On

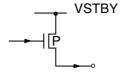

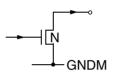

The IC provides an internal voltage supervision to generate an internal reset during power on or when the supply voltage goes below a certain level ( $V_{STBY}$  and  $V_{SUPD} < 2.75 \, V$  and/or  $V_{SUPO} < 4.2 \, V$ ). Also a clock supervision of the 5 MHz clock keeps the internal reset active until proper clock signal is detected (e.g three clock cycles with the correct period). When the reset Pin RESQ or the internal reset becomes active all counters and registers are set to zero. When the reset pin is released, the internal reset is still active for approximately 4  $\mu$ s. Then all registers are loaded with their default values listed in Table 3–5 on page 29. This initialization takes about 100  $\mu$ s.

The HOUT signal becomes high with the VSTBY supply after power-on, regardless of RESQ, VSUPP/D, and VSUPO. When a proper 5 MHz clock is established (e.g. 8 ms after VSTBY is powered up), HOUT outputs a 55 kHz pulse. This state remains until an  $I^2C$  command starts the self-start procedure (RAMP EN = 1).

Fig. 2-19: Reset timing

#### 3. Serial Interface

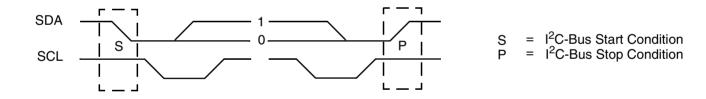

#### 3.1. I<sup>2</sup>C-Bus Interface

Communication between the DDP 3315C and the external controller is done via  $I^2C$ -bus. The DDP 3315C has an  $I^2C$ -bus slave interface and uses  $I^2C$  clock synchronization to slow down the interface if required.

Basically there are two classes of registers in the DDP 3315C.

The first class are directly addressable I<sup>2</sup>C registers. They are embedded in the hardware. These registers are 8 or 16 bits wide.

The second class are "XDFP-REGISTERS", which are used by the "XDFP" onchip controller. These registers are all 16 bits wide and support read/write operation. Communication with these registers requires I<sup>2</sup>C packets with a 16 bit XDFP-register address and 16 bit data.

Communication with both classes of registers (I<sup>2</sup>C and XDFP-REGISTERS) are performed via I<sup>2</sup>C. The format of the I<sup>2</sup>C telegram depends on which type of register is being accessed.

The I<sup>2</sup>C-bus chip address of the DDP 3315C is given below:

**Note:** The I<sup>2</sup>C address is subject to change.

| A6 | A5 | A4 | A4 A3 |   | A1 | A0 | R/W |

|----|----|----|-------|---|----|----|-----|

| 1  | 0  | 0  | 0     | 1 | 0  | 1  | 1/0 |

# 3.2. I<sup>2</sup>C Control and Status Registers

The I<sup>2</sup>C-bus interface uses one level of subaddress. First the bus address selects the IC, then a subaddress selects one of the internal registers. They have 8 or 16-bit data size; 16-bit registers are accessed by reading/writing two 8-bit data words. Writing is done by sending the device address first followed by the subaddress byte and one or two data bytes. For reading, the read address has to be transmitted first by sending the device write address followed by the subaddress a second start condition with the device read address and reading one or two bytes of data. Fig. 3-2 shows I2C protocol for read and write operations; the read operation requires an extra start condition and repetition of the chip address with read command set. Table 3-2 gives definitions of the I<sup>2</sup>C control and status registers.

Fig. 3–1: I<sup>2</sup>C-Bus protocol (MSB first, data must be stable while clock is high)

Write to I<sup>2</sup>C control register:

| S | 1000 101 | W | Ack | sub-addr. | Ack | 1 or 2 byte data | Ack | Р |

|---|----------|---|-----|-----------|-----|------------------|-----|---|

|---|----------|---|-----|-----------|-----|------------------|-----|---|

Read from I<sup>2</sup>C control register:

| , | S | 1000 101 | W | Ack | sub-addr. | Ack | S | 1000 101 | R | Ack | high byte data | Ack | low byte data | Nak | Р |

|---|---|----------|---|-----|-----------|-----|---|----------|---|-----|----------------|-----|---------------|-----|---|

|   |   |          |   |     |           |     |   |          |   |     |                |     |               |     |   |

W = 0 (Write bit) S = Start condition Ack = 0 (Acknowledge bit from DDP = grey or Controller = hatched)

Nak = 1 (Not acknowledge bit from Controller = hatched

Nak = 1 (Not acknowledge bit from Controller = hatched or indicating an error state from DDP = grey)

Fig. 3-2: I<sup>2</sup>C-Bus protocol

**Table 3–1:** I<sup>2</sup>C Register List in Numerical Order

| Ref.<br>Addr.<br>(hex) | Mode  | Register Name | Updated     |

|------------------------|-------|---------------|-------------|

| 10                     | 8-r/w | PSTR          | immediately |

| 11                     | 16-w  | PFC           | immediately |

| 12                     | 16-w  | dfpwr         | immediately |

| 13                     | 16-w  | dfprd         | immediately |

| 14                     | 8-r/w | LUTCTRL       | immediately |

| 15                     | 8-r/w | PSTRV         | immediately |

| 16                     | 16-w  | MINHY         | immediately |

| 17                     | 16-w  | ATVTY         | immediately |

| 18                     | 8-w   | MCRTL         | immediately |

| 1E                     | 8–r   | FBLSTAT       | immediately |

| 9F                     | 16–r  | HW_VER        | immediately |

Table 3–2: I<sup>2</sup>C Control and Status Registers in Functional Order

| Ref.<br>Addr.<br>(hex) | Bit Slice  | Min. | Max. | Function                | Default | Register Name |

|------------------------|------------|------|------|-------------------------|---------|---------------|

|                        |            |      |      | Hardware Version        |         |               |

| 9F                     |            |      |      | hardware version number |         | HW_VER        |

|                        | bit[3:0]   |      |      | minor version number    | 1       | HWVER_MIN     |

|                        | bit[7:4]   |      |      | major version number    | 2       | HWVER_MAJ     |

|                        | bit[15:8]  |      |      | not used                |         |               |

|                        |            |      |      | XDFP Interface          |         |               |

| 12                     |            |      |      | XDFP write address      |         |               |

|                        | bit[9:0]   | 0    | 511  | 10-bit XDFP RAM address | 0       | DFPWR         |

|                        | bit[15:10] |      | 0    | reserved, set to "0"    |         |               |

| 13                     |            |      |      | XDFP read address       |         |               |

|                        | bit[9:0]   | 0    | 511  | 10-bit XDFP RAM address | 0       | DFPRD         |

|                        | bit[15:10] |      | 0    | reserved, set to "0"    |         |               |

Table 3–2: I<sup>2</sup>C Control and Status Registers in Functional Order, continued

| Ref.<br>Addr.<br>(hex) | Bit Slice  | Min. | Max.                  | Function                                                                                                                                                            | Default | Register Name |  |  |

|------------------------|------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|--|--|

|                        | I.         |      |                       | Black Level Expander                                                                                                                                                |         |               |  |  |

| 17                     |            |      |                       | BLE activity control                                                                                                                                                |         | ATVTY         |  |  |

|                        | bit[3:0]   | 0    | 15                    | BLE tilt point                                                                                                                                                      | 7       | TILT          |  |  |

|                        | bit[5:4]   | 0    | 3<br>0<br>3           | BLE gain<br>maximum gain<br>minimum gain                                                                                                                            | 1       | BLEGAIN       |  |  |

|                        | bit[8:6]   | 0    | 7                     | 10 IRE black offset level (NTSC)                                                                                                                                    | 3       | IRE10         |  |  |

|                        | bit[11:9]  | 0    |                       | reserved, set to "0"                                                                                                                                                | 0       |               |  |  |

|                        | bit[14:12] | 0    | 7                     | noise margin for the activity measurement                                                                                                                           | 1       | AMPLTHR       |  |  |

|                        | bit[15]    | 0    |                       | reserved, set to "0"                                                                                                                                                |         |               |  |  |

| 18                     |            |      |                       | BLE mode control                                                                                                                                                    |         | MCRTL         |  |  |

|                        | bit[1:0]   | 0    | 3<br>0<br>1<br>2<br>3 | BLE mode 0: BLE off 1: autocontrast mode 2: dynamic mode 3: static mode                                                                                             | 2       | BLEMODE       |  |  |

|                        | bit[4:2]   | 0    | 7                     | static BLE break point                                                                                                                                              | 3       | SBLE          |  |  |

|                        | bit[7:5]   | 0    |                       | reserved, set to "0"                                                                                                                                                |         |               |  |  |

|                        |            |      |                       | Non-linear Colorspace Enhancer (NCE)                                                                                                                                | _       |               |  |  |

| 14                     |            |      |                       | NCE configuration register                                                                                                                                          |         | LUTCTRL       |  |  |

|                        | bit[1:0]   |      | 0<br>1<br>2<br>3      | input segment resolution 32 bits per step input range: 01023 16 bits per step input range: 0511 8 bits per step input range: 0255 4 bits per step input range: 0127 | 0       | XSEG          |  |  |

|                        | bit[2]     | 0    | 1                     | enables/disables LSB correction                                                                                                                                     | 0       | LSBCORDIS     |  |  |

|                        | bit[3]     | 0    | 1                     | enables/disables rounding always                                                                                                                                    | 0       | APWMDIS       |  |  |

|                        | bit[4]     | 0    | 1                     | y range extension bit                                                                                                                                               | 0       | YEX           |  |  |

|                        | bit[5]     | 0    | 1                     | bypass                                                                                                                                                              | 1       | NLBY          |  |  |

|                        | bit[7:6]   |      |                       | reserved, set to "0"                                                                                                                                                | 0       |               |  |  |

|                        |            |      |                       | Picture Frame Generator                                                                                                                                             |         |               |  |  |

| 11                     |            |      |                       | picture frame color, 12-bit wide                                                                                                                                    |         | PFC           |  |  |

|                        | bit[3:0]   | 0    | 15                    | blue amplitude                                                                                                                                                      | 0       | PFCB          |  |  |

|                        | bit[7:4]   | 0    | 15                    | green amplitude                                                                                                                                                     | 0       | PFCG          |  |  |

|                        | bit[11:8]  | 0    | 15                    | red amplitude                                                                                                                                                       | 0       | PFCR          |  |  |

|                        | bit[15:12] | 0    |                       | reserved, set to "0"                                                                                                                                                |         |               |  |  |

Table 3–2: I<sup>2</sup>C Control and Status Registers in Functional Order, continued

| Ref.<br>Addr. | Bit Slice | Min. | Max.        | Function                                                                          | Default | Register Name |

|---------------|-----------|------|-------------|-----------------------------------------------------------------------------------|---------|---------------|

| (hex)         |           |      |             | Angles Foot Blank Manites                                                         |         |               |

|               | 1         | T    | 1           | Analog Fast Blank Monitor                                                         | T       | I             |

| 1E            |           |      |             | fast blank signal status                                                          |         | FBLSTAT       |

|               | bit[0]    | 0    | 1           | FBLIN level low/high                                                              |         | FBLEV         |

|               | bit[1]    | 0    | 1           | FBLIN slope                                                                       |         | FBSLO         |

|               | bit[7:2]  | 0    |             | reserved, set to "0"                                                              |         |               |

|               |           |      | •           | Output Pins                                                                       | •       |               |

| 10            |           |      |             | output pin configuration                                                          |         | PSTR          |

|               | bit[1:0]  |      | 0 1         | pin driver strength, FIFO control maximum strength (7) medium strength (5)        | 0       | PSTSY         |

|               |           |      | 2           | minimum strength (3) tristated                                                    |         |               |

|               | bit[2]    | 0    | 1           | strong/weak (7/3) driver strength PWM1                                            | 0       | PSTPW1        |

|               | bit[3]    | 0    | 1           | strong/weak (7/3) driver strength PWM2                                            | 0       | PSTPW2        |

|               | bit[4]    | 0    | 1           | strong/weak (7/3) driver strength PWMV                                            | 0       | PSTPV2        |

|               | bit[5]    | 0    | 1           | disable/enable PWM output for EW Pin                                              | 0       | EWPWM         |

|               | bit[6]    | 0    | 1           | high/low active horizontal flyback input                                          | 0       | FLYPOL        |

|               | bit[7]    | 0    | 1           | strong/weak (7/3) driver strength DFVBL                                           | 0       | PSTDF         |

| 15            |           |      |             | output pin configuration                                                          |         | PSTRV         |

|               | bit[1:0]  | 0    | 3<br>0<br>3 | pin driver strength for EW<br>maximum strength (7)<br>minimum strength (4)        | 0       | PSTEW         |

|               | bit[3:2]  | 0    | 3<br>0<br>3 | pin driver strength for H-/V-SYNC<br>maximum strength (7)<br>minimum strength (4) | 0       | PSTHVS        |

|               | bit[7:4]  | 0    |             | reserved, set to "0"                                                              | 0       |               |

# 3.3. XDFP Control and Status Registers

The second class are "XDFP-REGISTERS", which are used by the XDFP onchip controller. Access to these registers is achieved by subaddressing. Writing to these registers is done by sending the device write address first, followed by the XDFP-write subaddress, two address bits for the desired XDFP-register and the two data bytes. For reading, the XDFP-register address has to be transmitted first by sending the device write address, followed by the XDFP-read subaddress and the two XDFP-register address bytes. Without sending a stop condition, reading of the addressed data is done by sending the device read address and reading two bytes of data. Fig. 3-3 shows I2C protocol for read and write operations. Table 3-5 on page 29 gives definitions of the XDFP control and status registers. If these registers are smaller than 16 bit the remaining bits should be 0 on write and read operations. Due to the internal architecture, the IC cannot react immediately to an I<sup>2</sup>C requests, which interacts with the onchip controller. The maximum response timing is appr. 20 ms. If the addressed controller is not ready for further transmissions on the I<sup>2</sup>Cbus, the clock line SCL is pulled low. This puts the current transmission into a wait state. After a certain period of time the clock line will be released and the interrupted transmission is carried on.

Table 3-3: XDFP read/write address

| XDFP Read address  | h'13 |

|--------------------|------|

| XDFP Write address | h'12 |

A hardware reset initializes all control registers to 0. The automatic chip initialization loads a selected set of registers with the default values given in Table 3–5 on page 29.

The register modes are

8/16- bit width

r read only register

w write only register

r/w write/read data register

Note: set unused bits to '0'!

The mnemonics used in the Micronas demo software are given in the last column.

# Write to XDFP control register:

|     |                 |     |       |                   |      |                 |       |               |     |                  |         |                | 1     |     |

|-----|-----------------|-----|-------|-------------------|------|-----------------|-------|---------------|-----|------------------|---------|----------------|-------|-----|

| - ( | 11000101        | ١٨/ | A old | XDFP-writeaddr.   | ۸ماد | highbyto addr   | مام ۸ | lowbyto addr  | ۸۵۷ | highbyto do      | to A ok | lowbyto data   | ا ماد | ь   |

| ١,  | ין ויטויטטטון כ | ٧V  | ACK   | ADIT - WITHEAUGI. | ACK  | migribyte addi. | ACK   | lowbyte addi. | ACK | i iligilibyte da | ia Ach  | l lowbyte data | ACK   | ı - |

# Read from XDFP control register:

| 010001011111111111111111111111111111111 |                    |                   | 1 1 0 100010 |         |                 |                   |       |

|-----------------------------------------|--------------------|-------------------|--------------|---------|-----------------|-------------------|-------|

| S 1000101 W Ack XDFP-readaddr.          | Ack highbyte addr. | Ack lowbyte addr. | Ack S 100010 | I R Ack | highbyte data A | ck lowbyte data N | Nak P |

W = 0 (Write bit) S = Start condition Ack = 0 (Acknowledge bit from DDP = grey P = 1 (Read bit) P = Stop condition or Controller = hatched)

Nak = 1 (Not acknowledge bit from Controller = hatched or

indicating an error state from DDP = grey)

Fig. 3-3: XDFP protocol

Table 3-4: XDFP Register List in Numerical Order

Ref. Mode Register Name Updated Addr. (hex) 20 16-r **VER** immediately 59 16-r/w BC immediately 6B 16-r/w CUTOFF\_R vertical 6C 16-r/w CUTOFF G vertical 6D 16-r/w **CUTOFF B** vertical 6E 16-r/w WDRIVE\_R vertical 6F 16-r/w WDRIVE\_G vertical 70 16-r/w WDRIVE B vertical 116 16-r/w **AMCTRL** vertical 117 16-r/w RCTRL0 vertical 11F 16-r/w GCTRL0 vertical 127 16-r/w **BCTRL0** vertical 131 **SCMODE** 16-r/w vertical 132 16-r/w **FFLIM** vertical 133 16-r/w SCINC<sub>1</sub> vertical 134 16-r/w SCINC2 vertical 135 **SCINC** 16-r/w vertical 136 16-r/w SCW1\_1 vertical 137 16-r/w SCW1\_2 vertical 138 16-r/w SCW1\_3 vertical 139 16-r/w SCW1\_4 vertical 13A 16-r/w SCW1\_5 vertical 13B 16-r/w SCW2\_1 vertical 13C 16-r/w SCW2\_2 vertical 13D 16-r/w SCW2\_3 vertical 13E 16-r/w SCW2\_4 vertical 13F 16-r/w SCW2\_5 vertical 14A 16-r/w LTI vertical 14B 16-r/w **SFIF** vertical 14E 16-r/w LTIMIX1 vertical 14F 16-r/w **BCT** vertical 152 16-r/w LTIMIX2 vertical 153 16-r/w **GCT** vertical

Table 3-4: XDFP Register List in Numerical Order

| Ref.<br>Addr.<br>(hex) | Mode   | Register Name | Updated    |

|------------------------|--------|---------------|------------|

| 154                    | 16-r/w | PFG           | vertical   |

| 157                    | 16-r/w | RCT           | vertical   |

| 158                    | 16-r/w | PBFB1         | vertical   |

| 15A                    | 16-r/w | BRM           | vertical   |

| 15B                    | 16-r/w | SVM2          | vertical   |

| 15C                    | 16-r/w | TML           | vertical   |

| 15F                    | 16-r/w | SVLIM         | vertical   |

| 160                    | 16-r/w | vbso          | vertical   |

| 164                    | 16-r/w | vbst          | vertical   |

| 167                    | 16-r/w | SVM1          | vertical   |

| 168                    | 16-r/w | PFGVE         | vertical   |

| 16A                    | 16-r/w | PK1           | vertical   |

| 16B                    | 16-r/w | DTICTRL       | vertical   |

| 16C                    | 16-r/w | PFGVB         | vertical   |

| 16E                    | 16-r/w | PK2           | vertical   |

| 16F                    | 16-r/w | CRCTRL        | vertical   |

| 170                    | 16-r/w | INFMT         | vertical   |

| 171                    | 16-r/w | HDRV          | vertical   |

| 172                    | 16-r/w | NEWLIN        | vertical   |

| 173                    | 16-r/w | HBST          | vertical   |

| 174                    | 16-r/w | HBSO          | vertical   |

| 175                    | 16-r/w | PFGHB         | vertical   |

| 176                    | 16-r/w | PFGHE         | vertical   |

| 178                    | 16-r/w | DFHB          | vertical   |

| 179                    | 16-r/w | DFHE          | vertical   |

| 17B                    | 16-r/w | PWM2          | vertical   |

| 17C                    | 16-r/w | PWM1          | vertical   |

| 17D                    | 16-r/w | DFDCTRL       | vertical   |

| 17E                    | 16-r/w | PWMV          | vertical   |

| 17E                    | 16-r/w | PWMV          | vertical   |

| 180                    | 16-r/w | HCTRL         | vertical   |

| 181                    | 16-r/w | POFS2         | horizontal |

| 182                    | 16-r/w | POFS3         | horizontal |

Table 3-4: XDFP Register List in Numerical Order

Ref. Mode Register Name Updated Addr. (hex) 183 16-r/w PKP2 horizontal 185 16-r/w PKP3 horizontal 187 16-r/w **ANGLE** horizontal 188 16-r/w **BOW** horizontal 18F 16-r/w **CENTER** vertical 190 16-r/w **AMPL** vertical 191 16-r/w ZOOM vertical 192 **VPOS** 16-r/w vertical 193 16-r/w LIN vertical 194 16-r/w **SCORR** vertical 195 16-r/w **VSYNWIN** vertical 196 16-r/w **LPFD** vertical 197 HOLDL 16-r/w vertical 198 16-r/w **FLYBL** vertical 19A 16-r/w **WIDTH** vertical 19B 16-r/w **TCORR** vertical 19C **CUSH** 16-r/w vertical 19D 16-r/w **CRNU** vertical 19E 16-r/w **CRNL** vertical 19F 16-r/w **CRNUS** vertical 1A0 16-r/w **CRNLS** vertical 1A6 16-r/w SATM vertical 1A7 CTM 16-r/w vertical 1A8 16-r/w MB2M vertical 1A9 16-r/w MB1M vertical 1AA 16-r/w MG2M vertical 1AB 16-r/w MG1M vertical 1AC 16-r/w MR2M vertical 1AD 16-r/w MR1M vertical 1AF 16-r/w **EHT\_THRES** horizontal 1B0 16-r/w EHT\_STC horizontal 1B1 16-r/w EHTV\_SA1 horizontal 1B2 16-r/w EHTV\_SA2 horizontal

Table 3-4: XDFP Register List in Numerical Order

| Ref.<br>Addr.<br>(hex) | Mode   | Register Name | Updated     |

|------------------------|--------|---------------|-------------|

| 1B3                    | 16-r/w | EHTH_SA1      | horizontal  |

| 1B4                    | 16-r/w | EHTH_SA2      | horizontal  |

| 1C0                    | 16-r/w | IBRM          | vertical    |

| 1C1                    | 16-r/w | MADCLAT       | vertical    |

| 1C2                    | 16-r/w | MCTRL         | vertical    |

| 1C3                    | 16-r/w | CUT_R         | vertical    |

| 1C4                    | 16-r/w | CUT_G         | vertical    |

| 1C5                    | 16-r/w | CUT_B         | vertical    |

| 1C6                    | 16-r/w | CUT_GAIN      | vertical    |

| 1C8                    | 16-r/w | WDR_R         | vertical    |

| 1C9                    | 16-r/w | WDR_G         | vertical    |

| 1CA                    | 16-r/w | WDR_B         | vertical    |